- 您现在的位置:买卖IC网 > Sheet目录369 > X28C512JIZ-12 (Intersil)IC EEPROM 512KBIT 120NS 32PLCC

X28C512, X28C513

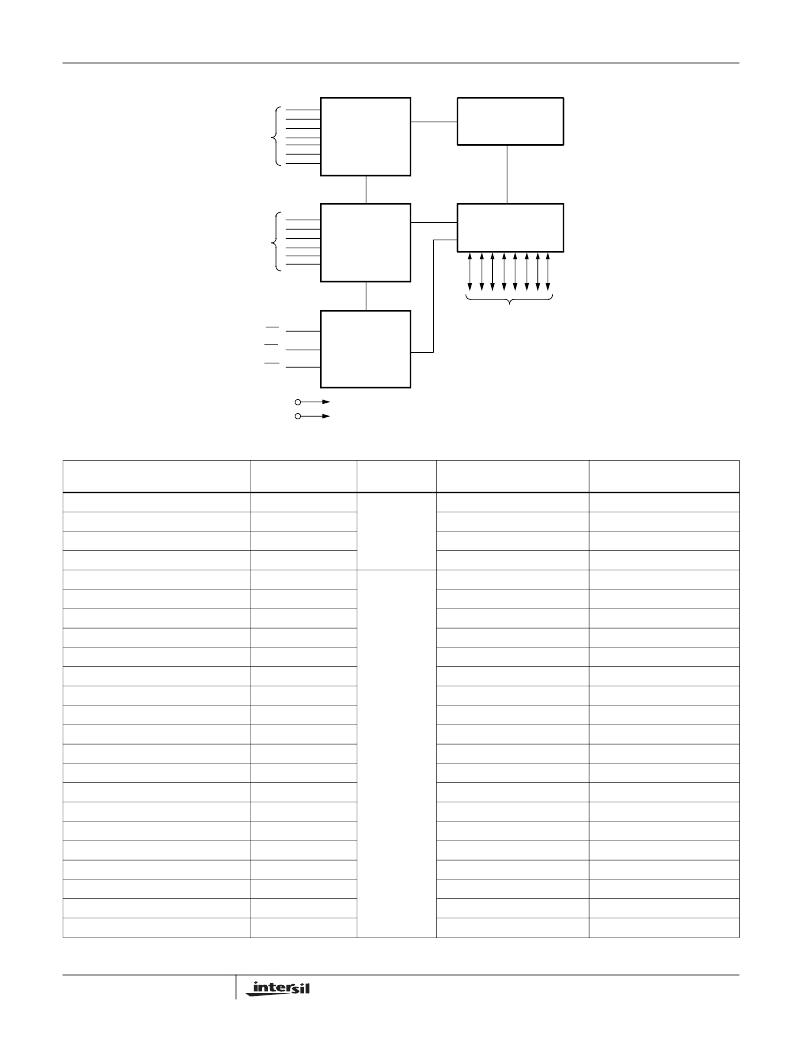

Block Diagram

512Kbit

A 7 -A 15

A 0 -A 6

X Buffers

Latches and

Decoder

Y Buffers

Latches and

EEPROM

Array

I/O Buffers

and Latches

Decoder

I/O 0 -I/O 7

CE

OE

WE

Control

Logic and

Timing

Data Inputs/Outputs

V CC

V SS

Ordering Information

ACCESS TIME

PART NUMBER

X28C512D

X28C512DM

X28C512J

X28C513EM

X28C512D-12

X28C512DI-12

X28C512DMB-12

X28C512FMB-12

X28C512J-12*

X28C512JZ-12* (See Note)

X28C512JI-12

X28C512JIZ-12* (See Note)

X28C512JM-12

X28C512KM-12

X28C512PI-12

X28C512RMB-12

X28C513EM-12

X28C513EMB-12

X28C513J-12*

X28C513JZ-12* (Note)

X28C513JI-12*

X28C513JIZ-12* (Note)

X28C513JM-12

PART MARKING

X28C512D

X28C512DM

X28C512J

X28C513EM

X28C512D-12

X28C512DI-12

X28C512DMB-12

X28C512FMB-12

X28C512J-12

X28C512J-12 Z

X28C512JI-12

X28C512JI-12 Z

X28C512JM-12

X28C512KM-12

X28C512PI-12

X28C512RMB-12

X28C513EM-12

X28C513EMB-12

X28C513J-12

X28C513J-12 Z

X28C513JI-12

X28C513JI-12 Z

X28C513JM-12

(ns)

-

120

TEMP RANGE (°C)

0 to +70

-55 to +125

0 to +70

-55 to +125

0 to +70

-40 to +85

Mil-STD-883

Mil-STD-883

0 to +70

0 to +70

-40 to +85

-40 to +85

-55 to +125

-55 to +125

-40 to +85

Mil-STD-883

-55 to +125

Mil-STD-883

0 to +70

0 to +70

-40 to +85

-40 to +85

-55 to +125

PACKAGE

32 Ld CERDIP

32 Ld CERDIP

32 Ld PLCC

32 Ld LCC

32 Ld CERDIP

32 Ld CERDIP

32 Ld CERDIP

32 Ld Flat Pack

32 Ld PLCC

32 Ld PLCC (Pb-free)

32 Ld PLCC

32 Ld PLCC (Pb-free)

32 Ld PLCC

36 Ld CPGA

32 Ld PDIP

32 Ld Flat Pack

32 Ld LCC

32 Ld LCC

32 Ld PLCC

32 Ld PLCC (Pb-free)

32 Ld PLCC

32 Ld PLCC (Pb-free)

32 Ld PLCC

2

FN8106.2

June 7, 2006

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

X28HC256SIZ-90

IC EEPROM 256KBIT 90NS 28SOIC

X28HC64JIZ-90

IC EEPROM 64KBIT 90NS 32PLCC

XCARD XK-1A

DEV KIT EVENT-DRIVEN PROC XS1-L1

XCARD XTAG-2

ADAPTER USB DEBUGGER JTAG XSYS2

XE8000EV101

EVAL BOARD FOR XE8801AMI027LF

XG4E-6431-S012

CONN PLUG 64POS 1A OPENED COVER

XLNRC

RAPID OUTPUT CONNECTOR

XLT80PT3

SOCKET TRAN ICE 80MQFP/TQFP

相关代理商/技术参数

X28C512JIZ-15

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5V, Byte Alterable EEPROM

X28C512JM-12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5V, Byte Alterable EEPROM

X28C512JM-15

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5V, Byte Alterable EEPROM

X28C512JM-20

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5V, Byte Alterable EEPROM

X28C512JM-25

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5V, Byte Alterable EEPROM

X28C512JM-90

制造商:XICOR 制造商全称:Xicor Inc. 功能描述:5 Volt, Byte Alterable E2PROM

X28C512JMB-12

制造商:XICOR 制造商全称:Xicor Inc. 功能描述:5 Volt, Byte Alterable E2PROM

X28C512JMB-15

制造商:XICOR 制造商全称:Xicor Inc. 功能描述:5 Volt, Byte Alterable E2PROM